# THC63LVD827-Z

#### LOW POWER / SMALL PACKAGE / 24Bit COLOR LVDS TRANSMITTER

#### **General Description**

The THC63LVD827-Z transmitter is designed to support pixel data transmission between Host and Flat Panel Display and Dual Link transmission between Host and Flat Panel Display up to 1080p/1920x1200 resolutions.

The THC63LVD827-Z converts 27bits (RGB 8 bits + Hsync, Vsync, DE) of CMOS/TTL data into LVDS (Low Voltage Differential Signaling) data stream. The transmitter can be programmed for rising edge or falling edge clocks through a dedicated pin.

For dual LVDS out, LVDS clock frequency of 87MHz, 51bits of RGB data are transmitted at an effective rate of 609Mbps per LVDS channel.

For single LVDS out, LVDS clock frequency of 174MHz, 27bits of RGB data are transmitted at an effective rate of 1218Mbps per LVDS channel.

21bits (RGB 6 bits + Hsync, Vsync, DE) mode is also selectable for 6bit color transmission with lower power.

#### **Features**

- Low power 1.8V CMOS design

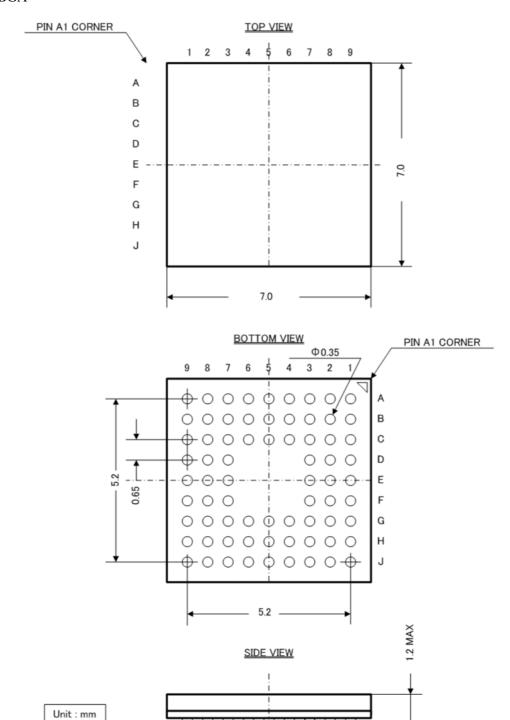

- 7mm x 7mm/72pin/0.65mm pitch/TFBGA package applicable to non-HDI PCB.

- Wide dot clock range, 10-174MHz, suited for TV Signal: up to 1080p(74.25MHz dual)

PC Signal: up to 1920x1200(77MHz dual)

- Supports 1.8V single power supply

- 1.8V/2.5V/3.3V TTL/CMOS inputs are supported by setting IOVCC=1.8V/2.5V/3.3V

- LVDS swing reducible by RS-pin to reduce both EMI and power consumption

- PLL requires No external components

- Flexible Input / Output mode

- 1. Single in / Dual LVDS out

- 2. Single in / Single LVDS out

- 3. Double edge Single in / Dual LVDS out

- 2 LVDS data mapping to simplify PCB layout

- · Power down mode

- Input clock triggering edge selectable by R/F pin

- 6bit / 8bit modes selectable by 6B/8B pin

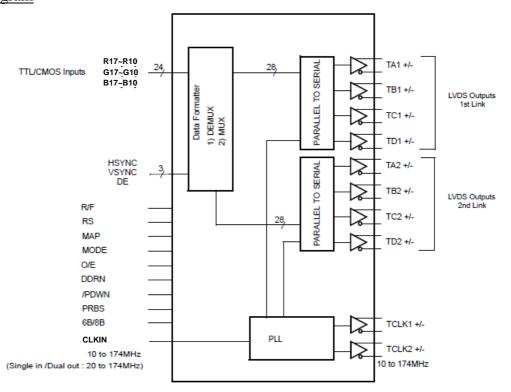

#### **Block Diagram**

Figure 1. Block Diagram

# Pin Diagram (top view)

# TOP VIEW

|        | 1    | 2    | 3           | 4          | 5           | 6    | 7          | 8     | 9          |   |

|--------|------|------|-------------|------------|-------------|------|------------|-------|------------|---|

| А      | TA1+ | TB1+ | TC1+        | TCLK1<br>+ | TD1+        | TA2+ | TB2+       | TC2+  | TCLK2<br>+ | А |

| В      | TA1- | TB1- | TC1-        | TCLK1      | TD1-        | TA2- | TB2-       | TC2-  | TCLK2<br>- | В |

| С      | PRBS | N/C  | Reservedl   | GND        | ACC<br>TAD2 | GND  | PLL<br>VCC | TD2-  | TD2+       | С |

| D      | R11  | R10  | VCC<br>LVDS |            |             |      | GND        | /PDWN | OÆ         | D |

| E      | R13  | R12  | GND         |            |             |      | MODE       | MAP   | DDRN       | E |

| F      | R15  | R14  | GND         |            |             |      | 6B/8B      | RS    | CLKIN      | F |

| G      | R17  | R16  | VCC         | GND        | VCC         | GND  | IOVCC      | R/F   | DE         | G |

| н      | G10  | G12  | G14         | G16        | B10         | B12  | B14        | B16   | VSYNC      | н |

| J      | G11  | G13  | G15         | G17        | B11         | B13  | B15        | B17   | HSYNC      | J |

| $\neg$ | 1    | 2    | 3           | 4          | 5           | 6    | 7          | 8     | 9          | T |

Figure 2. Pin Diagram

# Pin Description

**Table 1. Pin Description**

| Pin Name       | Pin #       | Type     | Description                                                                                                                                               |  |  |  |  |

|----------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TA1+,TA1-      | A1,B1       |          |                                                                                                                                                           |  |  |  |  |

| TB1+,TB1-      | A2,B2       |          | The 1st Link. The 1st pixel output data when Dual out. Output data when Single out.                                                                       |  |  |  |  |

| TC1+,TC1-      | A3,B3       |          |                                                                                                                                                           |  |  |  |  |

| TD1+, TD1-     | A5,B5       |          | Output data when Single out.                                                                                                                              |  |  |  |  |

| TCLK1+, TCLK1- | A4,B4       | LUDGOUT  | LVDS Clock Out for 1st Link.                                                                                                                              |  |  |  |  |

| TA2+,TA2-      | A6,B6       | LVDS OUT | LVDS Clock Out for 1st Link.  The 2nd Link.                                                                                                               |  |  |  |  |

| TB2+,TB2-      | A7,B7       |          | The 2nd Link. The 2nd pixel output data when Dual out.                                                                                                    |  |  |  |  |

| TC2+,TC2-      | A8,B8       |          | The 2nd pixel output data when Dual out.                                                                                                                  |  |  |  |  |

| TD2+, TD2-     | C9,C8       |          | LVDS Clock Out for 2nd Link.                                                                                                                              |  |  |  |  |

| TCLK2+, TCLK2- | A9,B9       |          | LVDS Clock Out for 2nd Link.                                                                                                                              |  |  |  |  |

| R17~R10        | G1,G2,F1,F2 |          |                                                                                                                                                           |  |  |  |  |

| KI7~KIU        | E1,E2,D1,D2 |          |                                                                                                                                                           |  |  |  |  |

| G17~G10        | J4,H4,J3,H3 | IN       | Pixel Data Inputs.                                                                                                                                        |  |  |  |  |

| <b>317 310</b> | J2,H2,J1,H1 | 111      | I moi zaua inputo                                                                                                                                         |  |  |  |  |

| B17~B10        | J8,H8,J7,H7 |          |                                                                                                                                                           |  |  |  |  |

|                | J6,H6,J5,H5 | 77.      |                                                                                                                                                           |  |  |  |  |

| DE             | G9          | IN       | Data Enable Input.                                                                                                                                        |  |  |  |  |

| VSYNC          | H9          | IN       | Vsync Input.                                                                                                                                              |  |  |  |  |

| HSYNC          | J9          | IN       | Hsync Input.                                                                                                                                              |  |  |  |  |

| CLKIN          | F9          | IN       | Clock Input.                                                                                                                                              |  |  |  |  |

| R/F            | G8          | IN       | Input Clock Triggering Edge Select. H: Rising edge, L: Falling edge                                                                                       |  |  |  |  |

| RS             | F8          | IN       | LVDS swing mode select.           RS         LVDS Swing(VoD, see Fig.7 and Fig.8)           H         350mV           L         200mV                     |  |  |  |  |

| MAP            | E8          | IN       | LVDS mapping table select. See Fig.12 and Fig.13.  MAP Mapping Mode H Mapping MODE1 L Mapping MODE2                                                       |  |  |  |  |

| MODE           | E7          | IN       | Pixel data mode. See Fig.10 and Fig.11.  MODE Modes H Single out (Single-in / Single-out) L Dual out (Single-in / Dual-out)                               |  |  |  |  |

| O/E            | D9          | IN       | Output enable H: Output enable. L: Output disable (all outputs are Hi-Z).                                                                                 |  |  |  |  |

| /PDWN          | D8          | IN       | Power Down enable H: Normal operation. L: Power down (all outputs are Hi-Z and all circuits are stand-by mode with minimum current (I <sub>TCCS</sub> )). |  |  |  |  |

| PRBS (*a)      | C1          | IN       | Must be tied to GND.                                                                                                                                      |  |  |  |  |

### Pin Description (Continued)

| Pin Name  | Pin#                     | Type    | Description                                                                                                                                                 |

|-----------|--------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved1 | C3                       | IN      | Must be tied to GND.                                                                                                                                        |

| 6B/8B     | F7                       | IN      | 6bit / 8bit mode select. H: 6bit mode (21bit mode), L: 8bit mode (27bit mode).                                                                              |

| DDRN      | E9                       | IN      | DDR function is active when MODE=L (Dual-out mode) H: DDR (Double Edge input) function disable (Fig.7). L: DDR (Double Edge input) function enable (Fig.8). |

| N/C       | C2                       | -       | Must be Open.                                                                                                                                               |

| VCC       | G3,G5                    |         | Power Supply Pins for digital circuitry.                                                                                                                    |

| IOVCC     | G7                       | Darrian | Power Supply Pins for IO inputs circuitry.                                                                                                                  |

| LVDSVCC   | C5,D3                    | Power   | Power Supply Pins for LVDS Outputs.                                                                                                                         |

| PLLVCC    | C7                       |         | Power Supply Pins for PLL circuitry.                                                                                                                        |

| GND       | F3,G4,G6,C4,<br>E3,C6,D7 | Ground  | Ground Pins.                                                                                                                                                |

<sup>(\*</sup>a): Setting the PRBS pin high enables the internal test pattern generator. It generates Pseudo-Random Bit Sequence of 2<sup>23</sup>-1.

The generated PRBS is fed into input data latches, encoded and serialized into LVDS OUT.

This function is normally to be used for analyzing the signal integrity of the transmission channel including PCB traces, connectors, and cables.

# Absolute Maximum Ratings

**Table 2. Absolute Maximum Rating**

| Parameter                                 | Min  | Max          | Unit |

|-------------------------------------------|------|--------------|------|

| Power Supply Voltage (IOVCC)              | -0.3 | +4.0         | V    |

| Power Supply Voltage (VCC,PLLVCC,LVDSVCC) | -0.3 | +2.1         | V    |

| CMOS/TTL Input Voltage                    | -0.3 | IOVCC+0.3    | V    |

| LVDS Transmitter Output Voltage           | -0.3 | LVDSVCC+0.3  | V    |

| Output Current                            | -50  | +50          | mA   |

| Junction Temperature                      | -    | +125         | °C   |

| Storage Temperature Range                 | -55  | +125         | °C   |

| Reflow Peak Temperature / Time            | -    | +260 / 10sec | °C   |

| Maximum Power Dissipation @+25°C          | -    | 1.3          | W    |

# **Recommended Operating Conditions**

**Table 3. Operating Condition**

| Symbol                      |                      | P                                     | arameter          |             | Min  | Тур               | Max  | Unit |

|-----------------------------|----------------------|---------------------------------------|-------------------|-------------|------|-------------------|------|------|

| Ta                          | Operating A          | perating Ambient Temperature          |                   |             |      | 25                | +105 | °C   |

| IOVCC                       | Power Supply Voltage |                                       |                   |             | 1.62 | 1.8<br>2.5<br>3.3 | 3.6  | V    |

| PLLVCC<br>LVDSVCC<br>VCC    | Power Supp           | Power Supply Voltage                  |                   |             |      | 1.8               | 1.98 | V    |

|                             |                      | MODE = L                              | Single Edge Input | Input       | 20   | -                 | 174  |      |

|                             |                      |                                       | (DDRN=H)          | LVDS Output | 10   | -                 | 87   |      |

|                             | Clock                | Dual - out                            | Double Edge       | Input       | 10   | -                 | 174  |      |

| $\mathbf{F}_{\mathbf{clk}}$ | Frequency            | Duai - Out                            | Input (DDRN=L)    | LVDS Output | 10   |                   | 174  | MHz  |

|                             |                      | MODE=H Input Single - out LVDS Output |                   | Input       | 10   | -                 | 174  |      |

|                             |                      |                                       |                   | 10          | -    | 174               |      |      |

### **Electrical Characteristics**

### CMOS/TTL (Pin type "IN") DC Specifications

Over recommended operating supply and temperature ranges unless otherwise specified.

**Table 4. CMOS/TTL DC Specifications**

| Symbol            | Parameter                     | Conditions          | Min        | Тур | Max        | Unit |

|-------------------|-------------------------------|---------------------|------------|-----|------------|------|

| $V_{IH18}$        | High Level Data Input Voltage | IOVCC-1 63V 1 09V   | 0.65*IOVCC | -   | IOVCC      | V    |

| $V_{\rm IL18}$    | Low Level Data Input Voltage  | - IOVCC=1.62V~1.98V | GND        | -   | 0.35*IOVCC | V    |

| $V_{\rm IH25}$    | High Level Data Input Voltage | IOVCC=2.3V~2.7V     | 1.7        | -   | IOVCC      | V    |

| V <sub>IL25</sub> | Low Level Data Input Voltage  | 10VCC=2.3V~2.7V     | GND        | -   | 0.7        | V    |

| V <sub>IH33</sub> | High Level Data Input Voltage | IOVCC=3.0V~3.6V     | 2.0        | -   | IOVCC      | V    |

| V <sub>IL33</sub> | Low Level Data Input Voltage  | 10VCC=3.0V~3.0V     | GND        | -   | 0.8        | V    |

| I <sub>INC</sub>  | Input Current                 | VIN=GND~IOVCC       | -10        | -   | +10        | μΑ   |

# LVDS Transmitter (Pin type "LVDS OUT") DC Specifications

Over recommended operating supply and temperature ranges unless otherwise specified.

**Table 5. LVDS Transmitter DC Specifications**

| Symbol          | Parameter                                                     | Conditions                           |                       | Min   | Тур  | Max   | Unit |

|-----------------|---------------------------------------------------------------|--------------------------------------|-----------------------|-------|------|-------|------|

| Von             | Diff. of IQ a AVI                                             | P 1000                               | Normal swing<br>RS=H  | 250   | 350  | 450   |      |

| V <sub>OD</sub> | Differential Output Voltage                                   | $R_L = 100\Omega$                    | Reduced swing<br>RS=L | 140   | 200  | 300   | mV   |

| ΔVου            | Change in V <sub>OD</sub> between complementary output states |                                      |                       | -     | -    | 35    |      |

| Voc             | Common Mode Voltage                                           | $R_L = 100\Omega$                    |                       | 1.125 | 1.25 | 1.375 | V    |

| ΔVος            | Change in V <sub>OC</sub> between complementary output states |                                      |                       |       | -    | 35    | mV   |

| Ios             | Output Short Circuit Current                                  | $V_{OUT}$ =GND, $R_L$ = 100 $\Omega$ |                       | -     | -    | 100   | mA   |

| Ioz             | Output TRI-State Current                                      | /PDWN=L,<br>V <sub>OUT</sub> = GNI   | O ~ LVDSVCC           | -20   | -    | +20   | μΑ   |

Electrical Characteristics (Continued)

#### **Power Supply Current**

Over recommended operating supply and temperature ranges unless otherwise specified.

**Table 6. Power Supply Current**

| Symbol            | Parameter             |                                                  | Condition                                   | s             | Typ(a)     | Max(b)     | Unit |

|-------------------|-----------------------|--------------------------------------------------|---------------------------------------------|---------------|------------|------------|------|

|                   |                       |                                                  |                                             | CLKIN=37MHz   | 24<br>(18) | 33<br>(26) |      |

|                   |                       |                                                  | MODE = H<br>Single - out                    | CLKIN=65MHz   | 29<br>(23) | 43<br>(37) |      |

|                   |                       |                                                  |                                             | CLKIN=72MHz   | 30<br>(24) | 46<br>(40) |      |

|                   |                       |                                                  | MODE                                        | CLKIN=89MHz   | 48 (36)    | 65<br>(53) |      |

|                   | Operating<br>Current  | R <sub>L</sub> =100Ω<br>CL=5pF<br>RS=H<br>(RS=L) | MODE = L Dual - out  DDRN = H DDR Input Off | CLKIN=119MHz  | 53<br>(41) | 75<br>(63) |      |

| I <sub>TCCW</sub> |                       |                                                  |                                             | CLKIN=139MHz  | 56<br>(44) | 82<br>(70) | mA   |

|                   |                       |                                                  |                                             | CLKIN=154MHz  | 58<br>(46) | 88<br>(76) |      |

|                   |                       |                                                  | MODE = L Dual - out  DDRN = L               | CLKIN=44.5MHz | 47<br>(35) | 64<br>(52) |      |

|                   |                       |                                                  |                                             | CLKIN=59.5MHz | 51<br>(39) | 74<br>(62) |      |

|                   |                       |                                                  |                                             | CLKIN=69MHz   | 54<br>(42) | 80<br>(68) |      |

|                   |                       |                                                  | DDR Input On                                | CLKIN=77MHz   | 56<br>(44) | 85<br>(73) |      |

| I <sub>TCCS</sub> | Power Down<br>Current |                                                  | , All Inputs = Fixed                        |               | 1          | 140        | μΑ   |

(a) All Typ. values are at VCC=1.8V, Ta=25°C. The 256 Grayscale Test Pattern inputs test for a typical display pattern. (b) All Max. values are at VCC=1.98V, Ta=105°C. Worst Case Test Pattern produces maximum switching frequency for all the LVDS outputs (Fig.3).

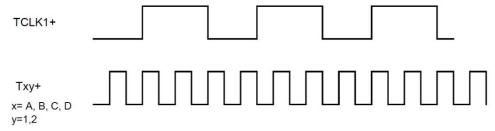

Figure 3. Test Pattern (LVDS Output Full Toggle Pattern)

# **Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

**Table 7. Switching Characteristics**

| Symbol              | Parameter                                          |                                               | Min                          | Тур                                    | Max                          | Unit |

|---------------------|----------------------------------------------------|-----------------------------------------------|------------------------------|----------------------------------------|------------------------------|------|

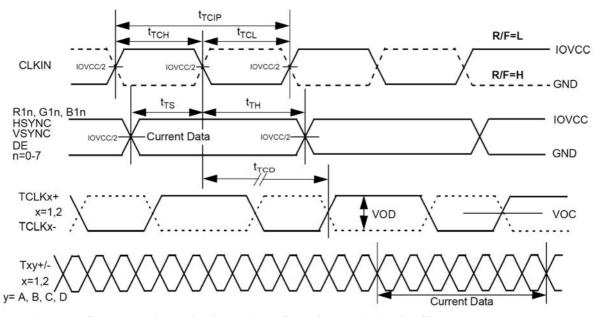

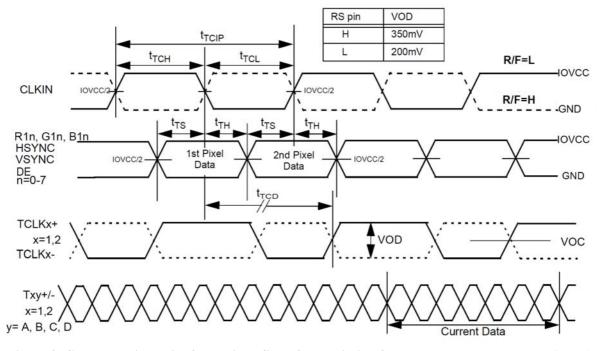

| $t_{TCIP}$          | CLKIN Period (Fig.7,8)                             |                                               | 5.75                         | -                                      | 100                          | ns   |

| t <sub>TCH</sub>    | CLKIN High Time (Fig.7,8)                          |                                               | 0.35t <sub>TCIP</sub>        | 0.5tтсір                               | 0.65t <sub>TCIP</sub>        | ns   |

| t <sub>TCL</sub>    | CLKIN Low Time (Fig.7,8)                           |                                               | 0.35t <sub>TCIP</sub>        | 0.5tтсір                               | 0.65t <sub>TCIP</sub>        | ns   |

| t <sub>TS</sub>     | TTL Data Setup to CLK IN (Fig.7,8                  | 0.8                                           | -                            | -                                      | ns                           |      |

| $t_{TH}$            | TTL Data Hold to CLK IN (Fig.7,8)                  | 1                                             | 0.8                          | -                                      | -                            | ns   |

|                     | CLKIN to TCLK+/-                                   | MODE=L,DDRN=H                                 | 9t <sub>TCIP</sub> +3.1      | -                                      | 9t <sub>TCIP</sub> +8.0      | ns   |

| t <sub>TCD</sub>    | Delay (Fig7,8)                                     | Others                                        | 5t <sub>TCIP</sub> +3.1      | -                                      | 5t <sub>TCIP</sub> +8.0      | ns   |

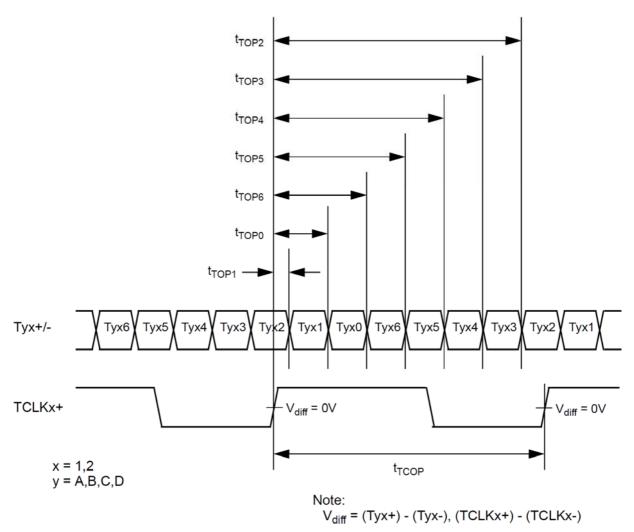

| t <sub>TCOP</sub>   | TCLK1,2 Period (Fig.6)                             |                                               | 5.75                         | -                                      | 100                          | ns   |

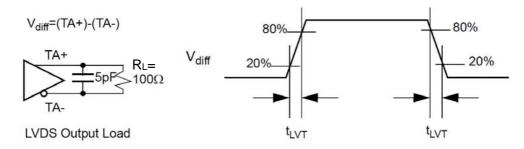

| t <sub>LVT</sub>    | LVDS Transition Time (Fig.4)                       |                                               | -                            | 0.6                                    | 1.5                          | ns   |

| t <sub>TOP1</sub>   | Output Data Position0 (Fig.9)                      |                                               | -0.15                        | 0.0                                    | +0.15                        | ns   |

| t <sub>TOP0</sub>   | Output Data Position1 (Fig.9)                      |                                               | $\frac{t_{TCOP}}{7}$ -0.15   | t <sub>TCOP</sub>                      | $\frac{t_{TCOP}}{7} + 0.15$  | ns   |

| $t_{TOP6}$          | Output Data Position2 (Fig.9)                      |                                               | $2\frac{t_{TCOP}}{7}$ -0.15  | 2 t <sub>TCOP</sub> 7                  | $2\frac{t_{TCOP}}{7} + 0.15$ | ns   |

| t <sub>TOP5</sub>   | Output Data Position3 (Fig.9)                      | $t_{TCOP} = 5.75 \text{ns} \sim 15 \text{ns}$ | $3\frac{t_{TCOP}}{7} - 0.15$ | $3\frac{t_{TCOP}}{7}$                  | $3\frac{t_{TCOP}}{7} + 0.15$ | ns   |

| $t_{TOP4}$          | Output Data Position4 (Fig.9)                      |                                               | $4\frac{t_{TCOP}}{7}-0.15$   | $4\frac{t_{TCOP}}{7}$                  | $4\frac{t_{TCOP}}{7} + 0.15$ | ns   |

| t <sub>TOP3</sub>   | Output Data Position5 (Fig.9)                      |                                               | $5\frac{t_{TCOP}}{7} - 0.15$ | 5 t <sub>TCOP</sub> 7                  | $5\frac{t_{TCOP}}{7} + 0.15$ | ns   |

| t <sub>TOP2</sub>   | Output Data Position6 (Fig.9)                      |                                               | $6\frac{t_{TCOP}}{7} - 0.15$ | $6\frac{t_{TCOP}}{7}$                  | $6\frac{t_{TCOP}}{7} + 0.15$ | ns   |

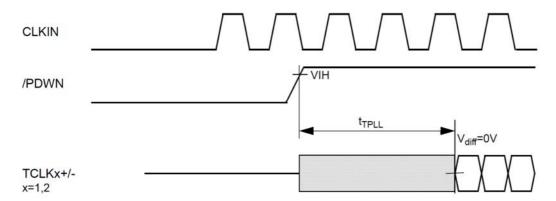

| $t_{\mathrm{TPLL}}$ | Phase Lock Time (Fig.5)                            |                                               | -                            | -                                      | 10.0                         | ms   |

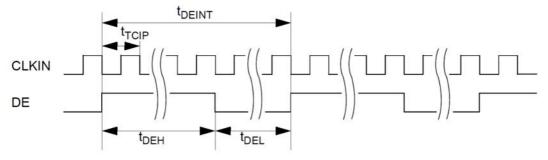

| $t_{ m DEINT}$      | DE Input Period (Fig.6) Dual out mode only(MODE=L) |                                               | 4t <sub>TCIP</sub>           | t <sub>TCIP</sub> *(2n) <sup>(a)</sup> | -                            | ns   |

| $t_{DEH}$           | DE Input Period (Fig.6) Dual out mode only(MODE=L) |                                               | 2t <sub>TCIP</sub>           | t <sub>TCIP</sub> *(2m) <sup>(a)</sup> | -                            | ns   |

| $t_{ m DEL}$        | DE Input Period (Fig.6) Dual out mode only(MODE=L) |                                               | 2t <sub>TCIP</sub>           | -                                      | -                            | ns   |

<sup>(</sup>a) Refer to Fig.6 for details.

#### **AC Timing Diagrams**

Figure 4. LVDS Output Load and Transition Time

Figure 5. PLL Lock Time

Note: Dual-out mode(MODE=L)

The period between rising edges of DE (t<sub>DEINT</sub>), high time of DE (t<sub>DEH</sub>) should always satisfy following equations.

$$t_{DEH} = t_{TCIP} * (2m)$$

$$t_{DEINT} = t_{TCIP} * (2n)$$

$$m, n = integer$$

Figure 6. Dual-out mode DE input timing

#### AC Timing Diagrams(Continued)

Figure 7. CLKIN Period, High/Low Time, Setup/Hold Timing for Single Edge Input Mode

MODE = H or DDRN = H

Figure 8. CLKIN Period, High/Low Time, Setup/Hold Timing for Double Edge Input Mode(DDR) MODE = L, DDRN = L

### AC Timing Diagrams(Continued)

**Figure 9. LVDS Output Data Position**

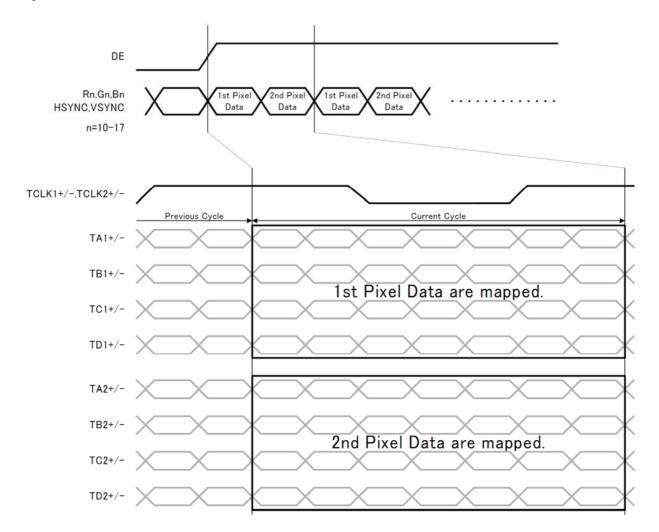

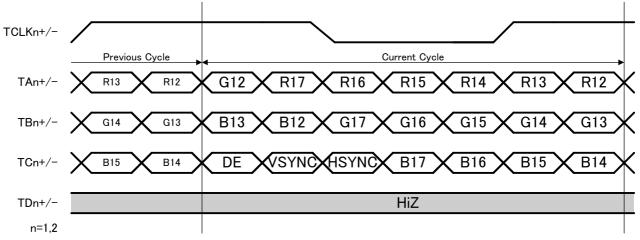

# Single-In / Dual-Out Mode (MODE = L)

Figure 10. Single-In / Dual-Out Mode (MODE = L)

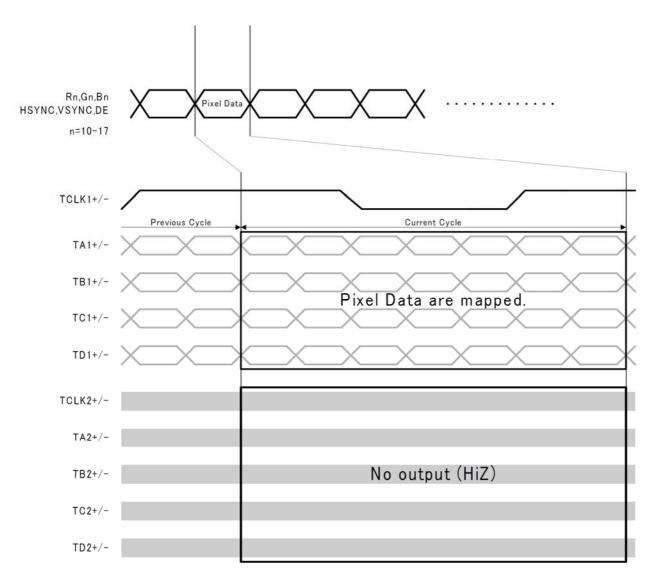

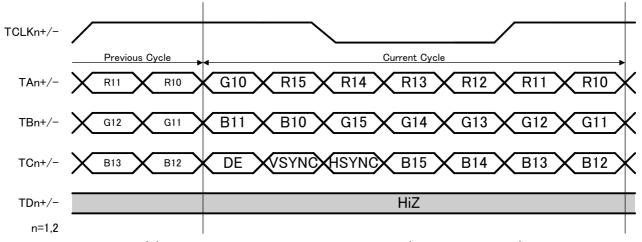

### Single-In / Single-Out Mode (MODE = H)

Figure 11. Single-In / Single-Out Mode (MODE = H)

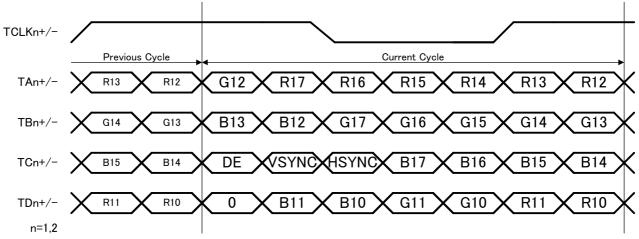

#### LVDS Data Mapping for 8 bit Mode (6B/8B = L)

(a) LVDS Data Mapping when MAP = H (Mapping Mode 1)

(b) LVDS Data Mapping when MAP = L (Mapping Mode 2)

Figure 12. LVDS Data Mapping for 8 bit Mode (6B/8B = L)

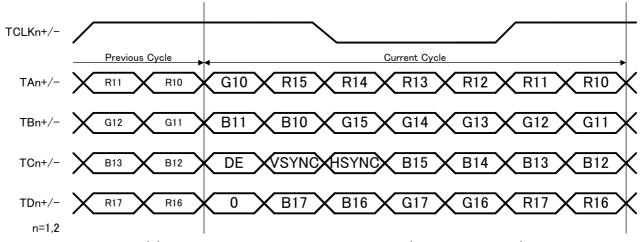

#### LVDS Data Mapping for 6 bit Mode (6B/8B = H)

(a) LVDS Data Mapping when MAP = H (Mapping Mode 1)

(b) LVDS Data Mapping when MAP = L (Mapping Mode 2)

Figure 13. LVDS Data Mapping for 6 bit Mode (6B/8B = H)

Note: Input pins which are not used in 6 bit Mode (R10-11,G10-11,B10-11 on Mapping Mode 1, R16-17,G16-17,B16-17 on Mapping Mode 2) can be H, L, or Open.

#### Note

1) Cable Connection and Disconnection Don't connect and disconnect the LVDS cable, when the power is supplied to the system.

#### 2) GND Connection

Connect the each GND of the PCB which THC63LVD827-Z and LVDS-Rx on it. It is better for EMI reduction to place GND cable as close to LVDS cable as possible.

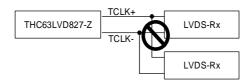

3) Multi Drop Connection Multi drop connection is not recommended.

Figure 14. Multi Drop Connection

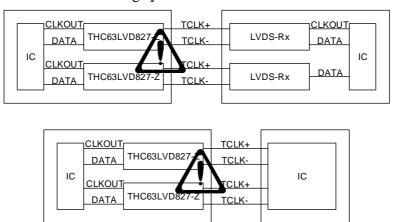

4) Asynchronous Use Asynchronous use such as following systems are not recommended.

Figure 15. Asynchronous Use

### **Package**

#### **TFBGA**

Figure 16. Package Diagram

- 0.35

#### **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without THine's prior permission is prohibited.

- 4. Note that even if infringement of any third party's industrial ownership should occur by using this product, THine will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

- 5. Product Application

- 5.1 Application of this product is intended for and limited to the following applications: audio-video device, office automation device, communication device, consumer electronics, smartphone, feature phone, and amusement machine device. This product must not be used for applications that require extremely high-reliability/safety such as aerospace device, traffic device, transportation device, nuclear power control device, combustion chamber device, medical device related to critical care, or any kind of safety device.

- 5.2 This product is not intended to be used as an automotive part, unless the product is specified as a product conforming to the demands and specifications of IATF16949 ("the Specified Product") in this data sheet. Thine accepts no liability whatsoever for any product other than the Specified Product for it not conforming to the aforementioned demands and specifications.

- 5.3 THine accepts liability for demands and specifications of the Specified Product only to the extent that the user and THine have been previously and explicitly agreed to each other.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 9. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act.

- 10. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses.

# THine Electronics, Inc.

sales@thine.co.jp https://www.thine.co.jp