# **THCS253**

I2C/GPIO High Speed Bus Signal Transceiver

System Design Guidelines

# Contents

| Contents                                                         | 2 |

|------------------------------------------------------------------|---|

| Example 1. I/O extension, Up/Down Stream synchronous mode        |   |

| Example 2. I/O & I2C extension, Up/Down Stream asynchronous mode |   |

| Example 3. I/O expansion with I2C                                |   |

| Design Guidelines for Power Supply                               |   |

| Design Guideline for High-Speed Signal                           |   |

| Notices and Requests                                             |   |

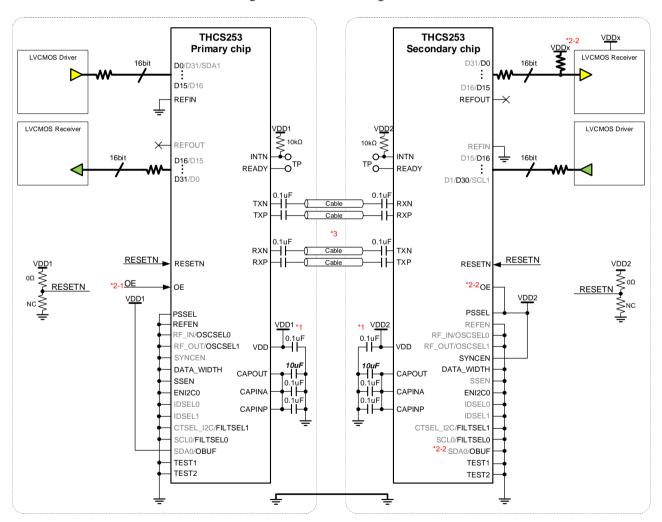

#### Example 1. I/O extension, Up/Down Stream synchronous mode

The primary chip performs parallel/serial conversion of input data using either the clock signal input to the REFIN pin or the built-in oscillator clock signal, whichever is selected, and outputs it from the TXP/N pin as a clock embedded serial signal. Secondary chip set to synchronous mode (SYNCEN pin = High) operate with clock signals regenerated from clock-embedded serial signals input to both the serial/parallel conversion circuit and the parallel/serial conversion circuit on the RXP/N pin. The Up/Down Stream will therefore have the same transmission bit rate.

Example 1 is an example of transmitting 16-bit GPIO data sampled asynchronously by the 20 MHz built-in oscillator clock on the Primary chip to the Secondary chip, and transmitting 16-bit GPIO data sampled asynchronously by the 20 MHz clock regenerated on the Secondary chip set to synchronous mode. This is an example of transmitting 16-bit GPIO data sampled asynchronously by a 20 MHz clock regenerated by the Secondary chip set to synchronous mode to the Primary chip.

When I2C is not used, all THCS253 settings are made at the setting terminals.

- $\blacksquare$  Power supply (\*1)

- The Primary chip (VDD1) and Secondary chip (VDD2) can be used with different supply voltages.

- Data output control in start-up sequences

- If I2C is not used, there are two options.

- Output enable control by OE pin (\*2-1)

- Set to open drain output and pull-up with receive side power supply (\*2-2)

- Disposal of unused terminals

Unused inputs should be fixed Low and outputs should be open.

- Cable for connection between Primary chip and Secondary chip (\*3)

Use twisted pair cables with a differential impedance of  $100~\Omega$ . Impedance error should be within  $\pm 10\%$ , but this is not a limitation if the signal waveform observed near the RXP/RXN terminals meets the Eye opening described in the datasheet.

When unshielded twisted pair cables are bundled with other signal lines or power lines, data errors may occur due to crosstalk between the lines, resulting in malfunctions. Twisted pair cables must be shielded for each pair.

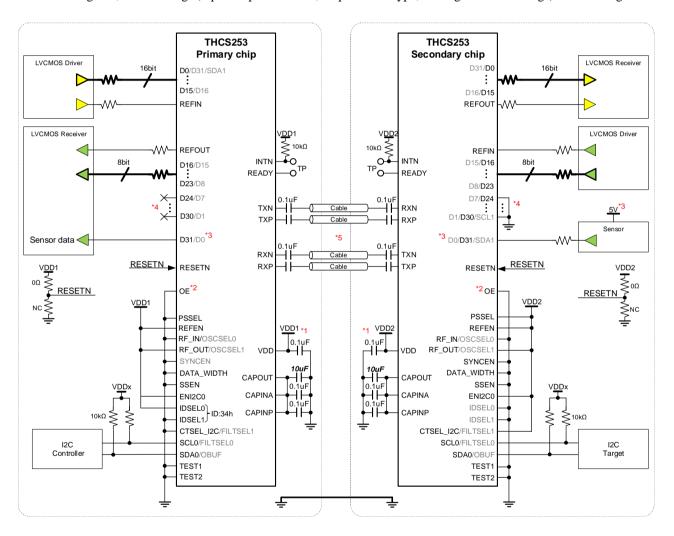

# Example 2. I/O & I2C extension, Up/Down Stream asynchronous mode

The primary chip and secondary chip perform parallel/serial conversion with the REFIN pin input clock signal or the internal oscillator clock signal selected by each chip, and output from the TXP/N pin as clock embedded serial signals. Therefore, the bit rate of the Up/Down stream signal is based on the clock signal frequency selected for each chip.

Example 2 shows an example of transmitting I2C data in addition to GPIO data sampled at the falling edge of the clock signal input to each REFIN pin.

When using I2C, some settings (input/output direction, output buffer type, and digital filter settings) are set in registers.

- $\blacksquare$  Power supply (\*1)

- The Primary chip (VDD1) and Secondary chip (VDD2) can be used with different supply voltages.

- Data output control in start-up sequences (\*2)

By fixing the OE pin to Low, all GPIO pins are disabled (Hi-Z) in the initial state immediately after power-on, avoiding unnecessary voltage application to the connected devices. From this state, set the input/output polarity and output buffer type of each GPIO pin using the GPIO\_OEN and GPIO\_OBUF registers, and then set the OVERRIDE\_OE register to "1" to enable GPIO, overriding the register setting over the OE pin setting.

Step 1. All outputs disabled by OE pin = Low (Hi-Z)

Step 2. GPIO\_OEN, GPIO\_OBUF, Set GPIO\_I\_FILTEN register as needed

Step 3. OVERRIDE OE register is set to "1"

### ■5V Tolerant I/O、Voltage Level Conversion (\*3)

There are up to four-5V input and output pins each. In the above example, a signal output from a 5V driven sensor is input to the 5V input terminal on the secondary chip side and output from the primary chip side at VDD1 voltage for 5V to VDD1 level conversion.

To use the 5V tolerant output pin as a 5V signal output, set the corresponding pin as an open drain and pull up to 5V externally.

#### ■ Disposal of unused terminals (\*4)

Unused inputs should be fixed Low and outputs should be open.

#### ■ Cable for connection between Primary chip and Secondary chip (\*5)

Use twisted pair cables with a differential impedance of  $100~\Omega$ . Impedance error should be within  $\pm 10\%$ , but this is not a limitation if the signal waveform observed near the RXP/RXN terminals meets the Eye opening described in the datasheet.

When unshielded twisted pair cables are bundled with other signal lines or power lines, data errors may occur due to crosstalk between the lines, resulting in malfunctions. Twisted pair cables must be shielded for each pair.

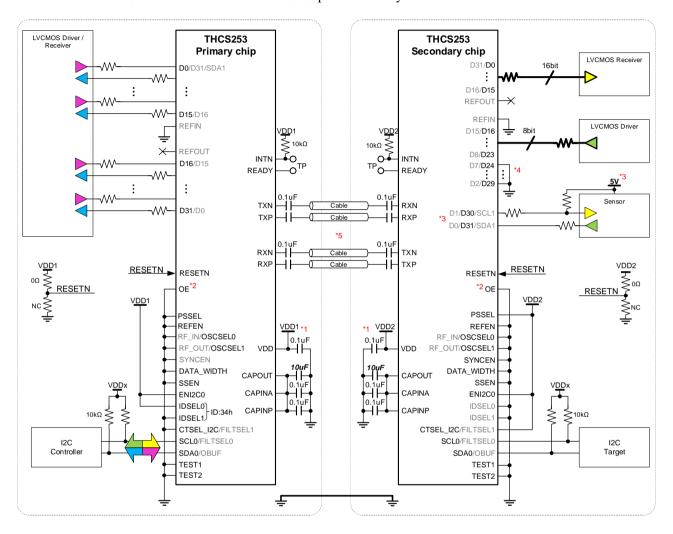

#### Example 3. I/O expansion with I2C

This mode uses I2C to control the state of each GPIO pin individually.

- $\blacksquare$  Power supply (\*1)

- The Primary chip (VDD1) and Secondary chip (VDD2) can be used with different supply voltages.

- Data output control in start-up sequences (\*2)

By fixing the OE pin to Low, all GPIO pins are disabled (Hi-Z) in the initial state immediately after power-on, avoiding unnecessary voltage application to the connected devices. From this state, set the input/output polarity and output buffer type of each GPIO pin using the GPIO\_OEN and GPIO\_OBUF registers, and then set the OVERRIDE\_OE register to "1" to enable GPIO, overriding the register setting over the OE pin setting.

- Step 1. All outputs disabled by OE pin = Low (Hi-Z)

- Step 2. I2C EXPAND register is set to "1"

- Step 3. GPIO\_OEN、GPIO\_OBUF, Set GPIO\_I\_FILTEN register as needed

- Step 4. OVERRIDE\_OE register is set to "1"

- ■5V Tolerant I/O、Voltage Level Conversion (\*3)

There are up to four-5V input and output pins each. In the above example, a signal output from a 5V driven sensor is input to the 5V input terminal on the secondary chip side and output from the primary chip side at

#### VDD1 voltage for 5V to VDD1 level conversion.

To use the 5V tolerant output pin as a 5V signal output, set the corresponding pin as an open drain and pull up to 5V externally.

- Disposal of unused terminals (\*4)

Unused inputs should be fixed Low and outputs should be open.

- Cable for connection between Primary chip and Secondary chip (\*5)

Use twisted pair cables with a differential impedance of  $100~\Omega$ . Impedance error should be within  $\pm 10\%$ , but this is not a limitation if the signal waveform observed near the RXP/RXN terminals meets the Eye opening described in the datasheet.

When unshielded twisted pair cables are bundled with other signal lines or power lines, data errors may occur due to crosstalk between the lines, resulting in malfunctions. Twisted pair cables must be shielded for each pair.

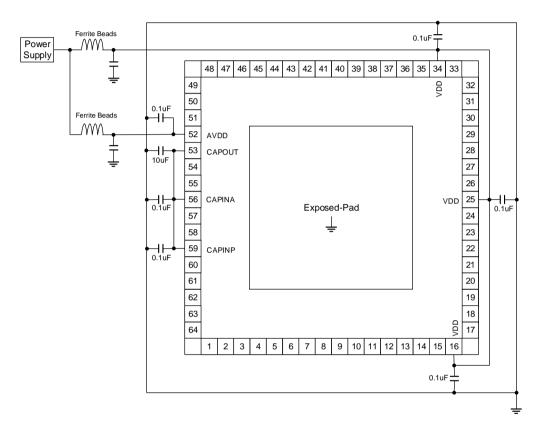

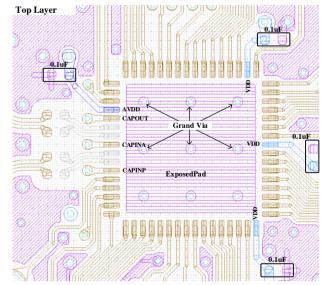

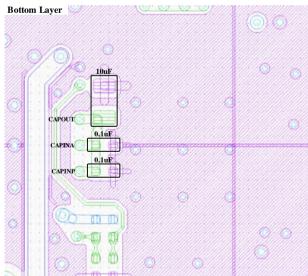

## **Design Guidelines for Power Supply**

Insert filters (Ferrite Beads and Capacitors) in the Power Supply (VDD and AVDD).

And insert Bypass Capacitor (0.1uF) in the Power Supply pins.

This device is equipped with a 1.2V built-in regulator.

Insert Bypass Capacitors (CAPOUT: 10uF and CAPINA/CAPINP: 0.1uF) also for this regulator.

Bypass Capacitors should be attached just near the device. Insert the GND-Via to the Exposed-Pad to strengthen.

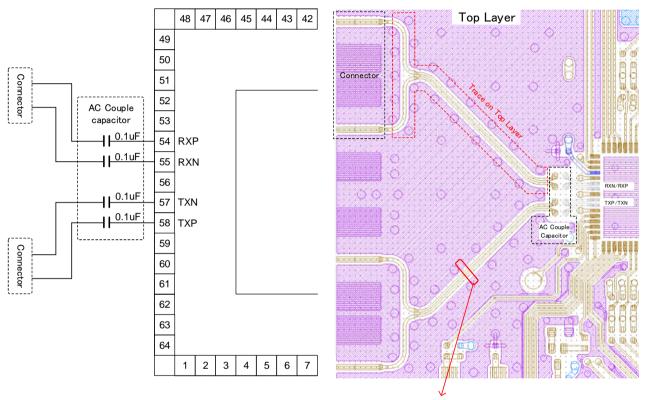

#### **Design Guideline for High-Speed Signal**

TXP/TXN and RXP/RXN are differential pairs of high-speed serial signals.

Differential pairs should be closely spaced and coupled to eliminate common mode noise.

Also, differential should be designed as  $100\Omega$  differential characteristic impedance (Zdiff).

The following is an example of microstrip line design.

The high-speed signal lines trace in only single layer.

The AC coupled capacitors should be attached just near the device.

Differential signal traces (Microstrip Lines)

#### **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without THine's prior permission is prohibited.

- 4. Note that even if infringement of any third party's industrial ownership should occur by using this product, THine will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

#### 5. Product Application

- 5.1 Application of this product is intended for and limited to the following applications: audio-video device, office automation device, communication device, consumer electronics, smartphone, feature phone, and amusement machine device. This product must not be used for applications that require extremely high-reliability/safety such as aerospace device, traffic device, transportation device, nuclear power control device, combustion chamber device, medical device related to critical care, or any kind of safety device.

- 5.2 This product is not intended to be used as an automotive part, unless the product is specified as a product conforming to the demands and specifications of IATF16949 ("the Specified Product") in this data sheet. Thine accepts no liability whatsoever for any product other than the Specified Product for it not conforming to the aforementioned demands and specifications. 5.3 Thine accepts liability for demands and specifications of the Specified Product only to the extent that the user and Thine have been previously and explicitly agreed to each other.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 9. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act.

- 10. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses.